# Safe-Operating Areas (SOAs) for Reliable High-Voltage Analog Devices

J.W. McPherson, Ph.D.

IEEE Fellow

Texas Instruments Senior Fellow Emeritus

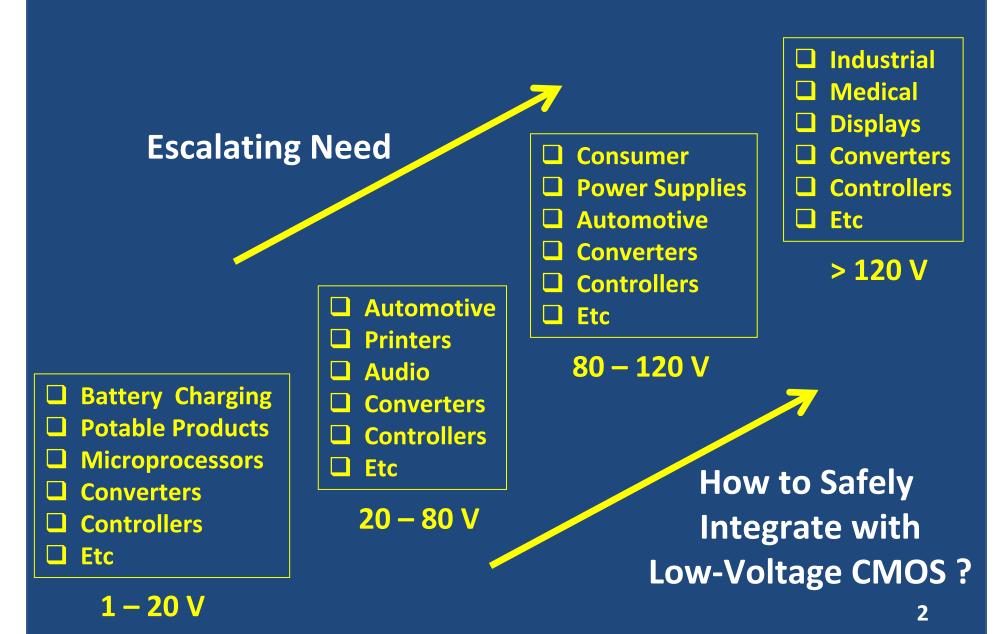

# Many Uses For High-Voltage Analog

# **Fundamental Reliability Physics Limitations**

| Fu            | Indamental Device Operational Issues at t=0                              |

|---------------|--------------------------------------------------------------------------|

|               | Silicon Avalanche Breakdown Field: 0.2-0.8 MV/cm                         |

|               | SiO <sub>2</sub> Breakdown Field: 10-15 MV/cm                            |

|               | Melting Temperature of Metals: Al(660°C), Cu(1083°C)                     |

|               | Fusing Current Density for Metals: ~ 2x10 <sup>7</sup> A/cm <sup>2</sup> |

|               | BVdss and BVii Limitations                                               |

|               | Latch-Up /ESD                                                            |

| Fu            | ındamental Device Reliability Issues for TF=10yrs@105°C                  |

|               | Electromigration (EM)                                                    |

|               | Stress Migration (SM)                                                    |

|               | Time-Dependent Dielectric Breakdown (TDDB)                               |

| $\overline{}$ |                                                                          |

| Ш             | Hot Carrier Injection(HCI)                                               |

|               | Hot Carrier Injection(HCI)  Negative-Bias Temperature Instability (NBTI) |

|               |                                                                          |

# Safe-Operating Areas (SOAs)

- Electrical SOA (e-SOA)

- Short Term Issues: BVdss, BVii, Latch-up, ESD

- Thermal SOA (T-SOA)

- Medium Term Issues: Power Density and Dissipation

- Reliability SOA (R-SOA)

- Long Term Issues: TDDB, HCI, NBTI, EM, SM, SEU

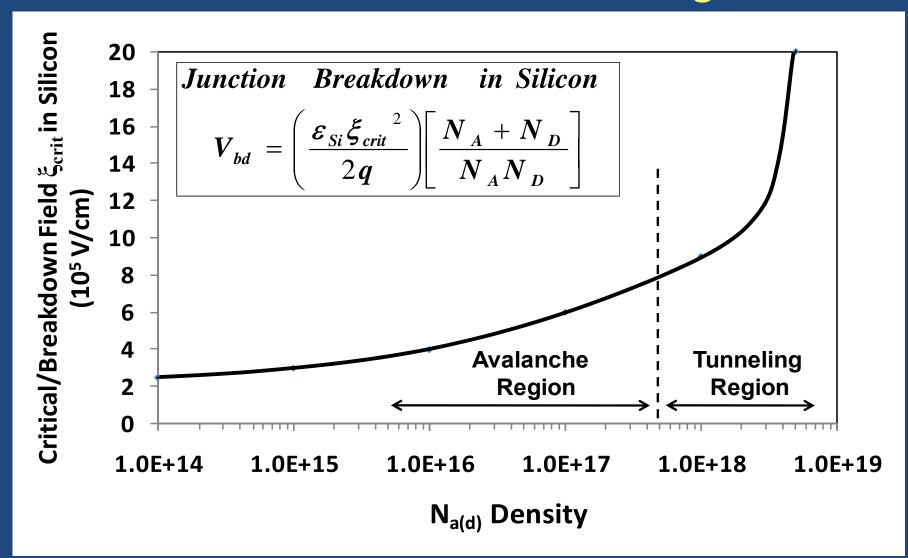

### **Critical Electric Field for Avalanching in Silicon**

Critical field (~0.2-0.8MV/cm) for avalanching must be avoided ! 5

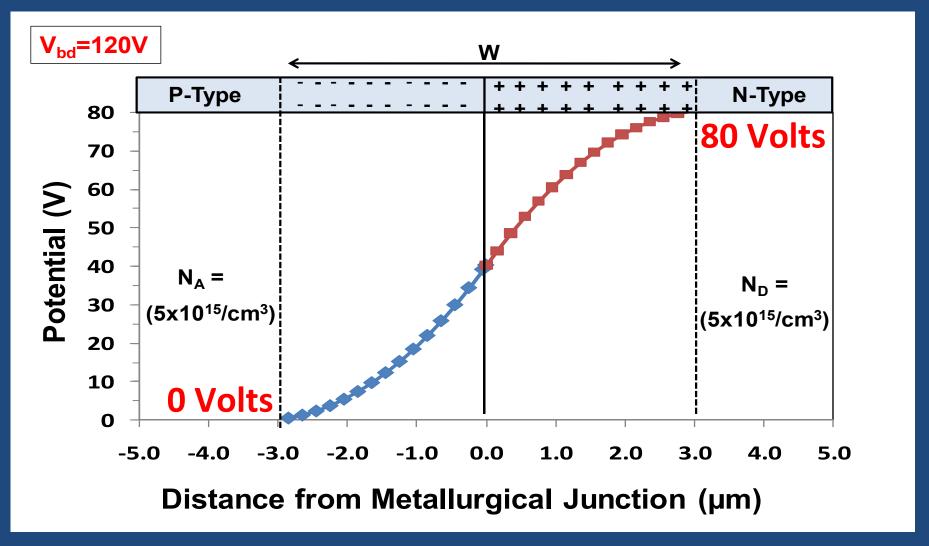

## **Voltage Drop Across Junction Depletion-Region**

Can safely drop large voltages across junction depletion-regions

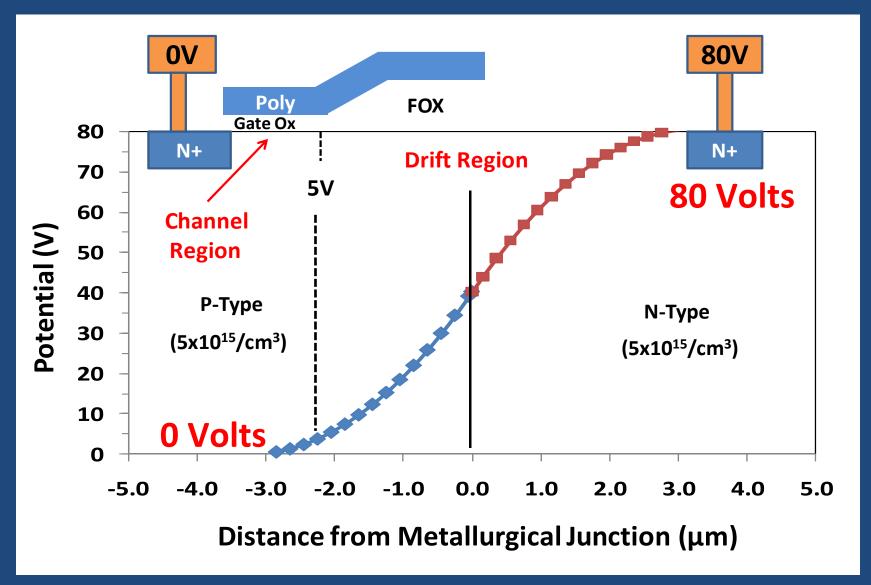

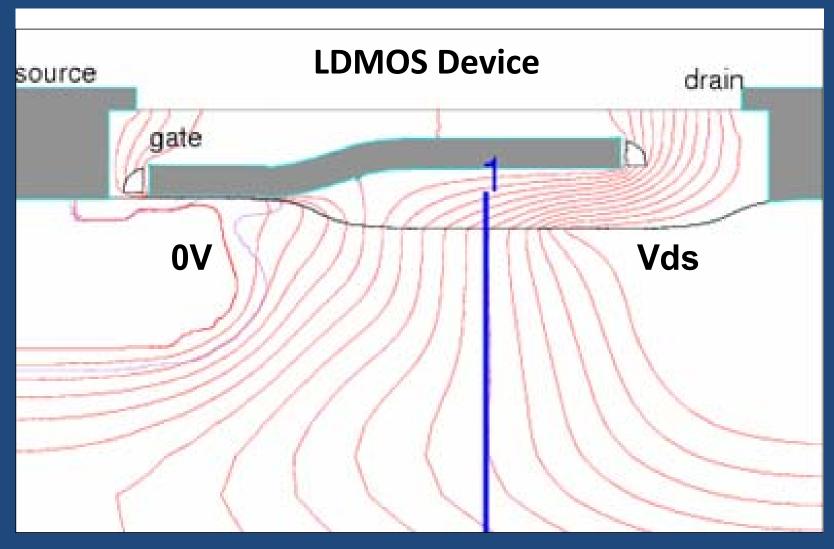

# e-SOA 5V-CMOS with 80V Drain Extension

# **Full Simulation of Voltage Drop**

Note: Voltage drop from drain to source

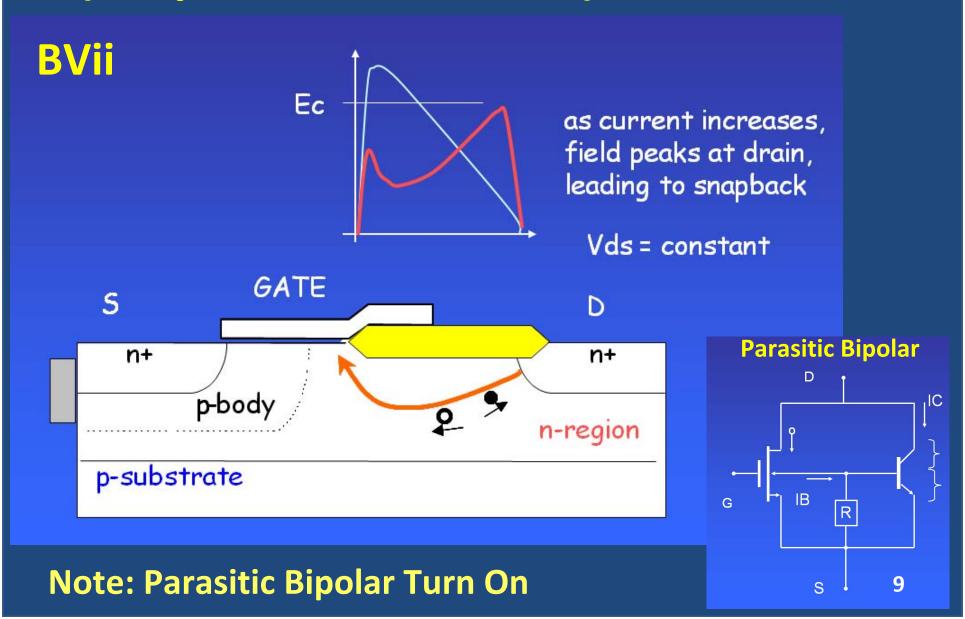

# (Snapback/Breakdown) Performance

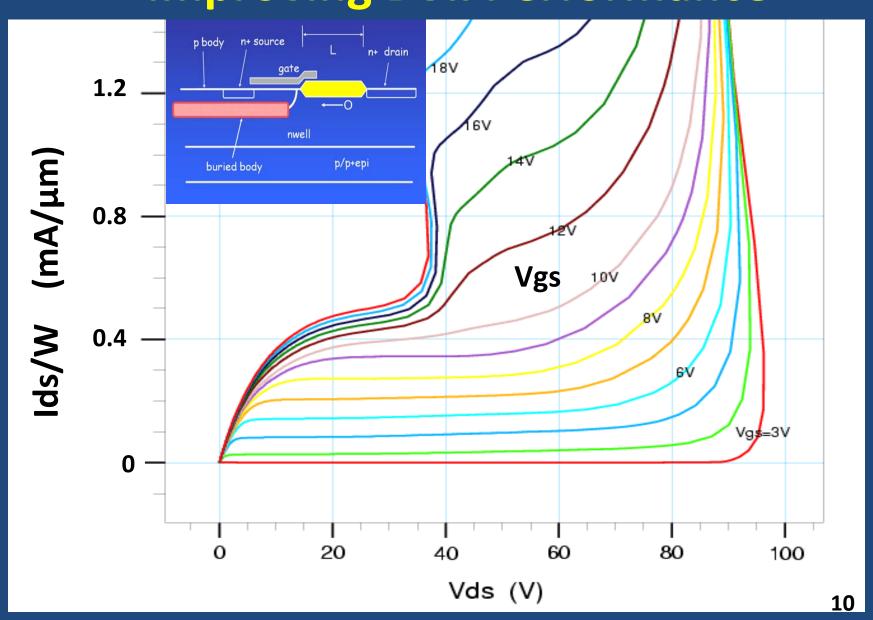

# **Improving BVii Performance**

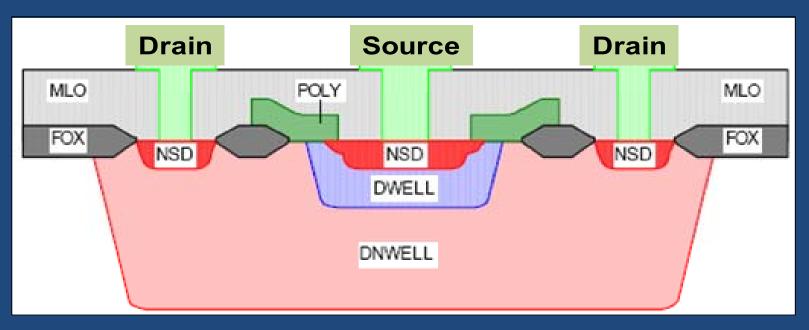

# **Fully Integrated LDMOS Device**

# What About Long-Term Reliability?

Now that we know how to build H-V devices in low-voltage CMOS that work safely at time zero (e-SOA) --- will they last for 10 yrs at 105°C?

### **Other Considerations:**

- ☐ Thermal SOA (T-SOA)

- □ Reliability SOA (R-SOA)

### T-SOA

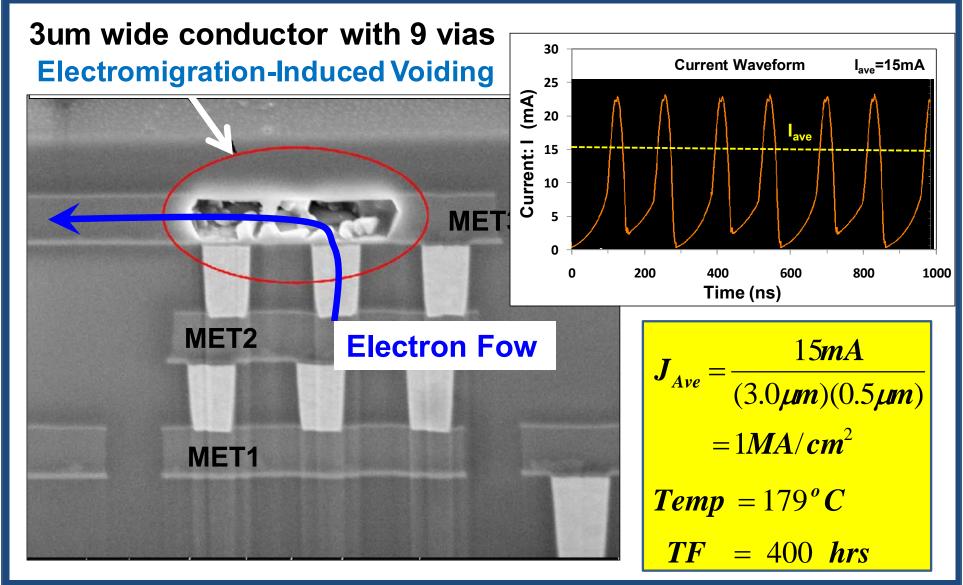

# **Electromigation in a Power Interconnects**

T-SOA

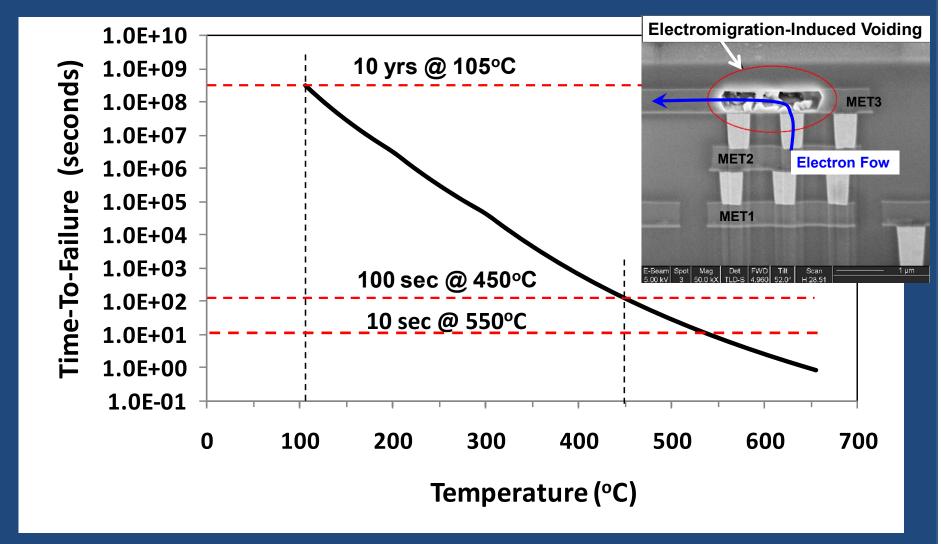

Metal Electromigration Lifetime Versus Temperature

Note: Metal migration (normally requiring 10yrs at 105°C) occurs within ~100sec at 450°C or ~10sec at 550°C.

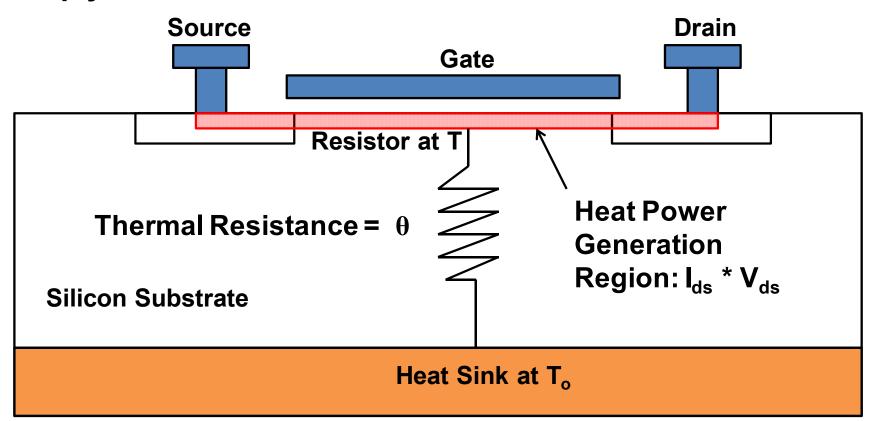

# T-SOA Steady State Heat Flow

Remember ---- for Joule heating analysis, the MOSFET is simply a Gate-Controlled Resistor

In Steady State:  $\Delta T = \theta \bullet Power = \theta \bullet (I_{ds}V_{ds})$

Thermal resistance  $\theta$  is normally expressed in °C/Watt

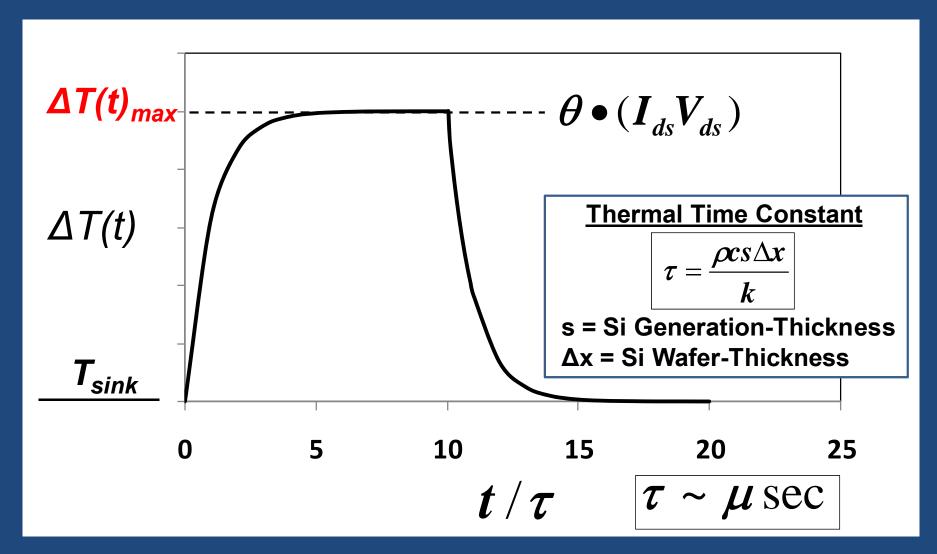

# T-SOA Transient Heat Flow

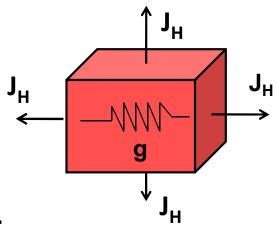

### **Heat Generation = Heat Absorbed + Heat Transferred**

g = generation of heat per unit volume = J<sub>Q</sub>E

J<sub>H</sub> = flux of heat out of unit volume

### **Conservation of Energy:**

Power Density Input = Power Density Absorbed + Power Density Transferred

$$g(t) = \rho c \frac{\partial T}{\partial t} + \vec{\nabla} \cdot \vec{J}_H$$

where:

$\vec{J}_H = -k\vec{\nabla}T$ ,  $k = thermal\ conductivity$ ,  $c = specific\ heat$ ,  $\rho = mass\ density$

$$k_{Si} = 83.7 \frac{W}{{}^{o}C m}$$

;  $\rho_{Si} = 2.33 \times 10^{3} \frac{kg}{m^{3}}$ ;  $c_{Si} = 6.78 \times 10^{2} \frac{W \sec}{{}^{o}C kg}$

#### T-SOA

## **Temperature Rise/Fall Times for Resistors in Silicon**

Note: 1ms pulses should reach ~ thermal equilibrium

#### **T-SOA**

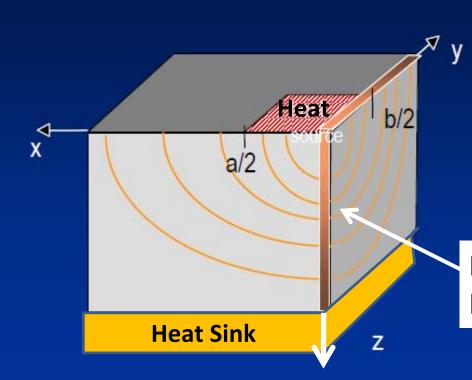

# **Transient Thermal Modeling**

$$k = 0.84 \text{ W/cm}^{\circ}\text{C}$$

$$\alpha = k/(\rho c)$$

$= 0.5 \text{ cm}^2/\text{s}$

Most of Thermal-Gradient/

Heat-Flow is in Vertical Direction

$$\Delta T(x, y, z, t) = \frac{\alpha}{k} \int_{0}^{t} \frac{dP(t')}{\left[4\pi\alpha(t - t')\right]^{1.5}} \times \exp\left[-\frac{r^2}{4\alpha(t - t')}\right] dt'$$

[IEEE-TED, vol. 48, #12, Dec 2001, pp. 2796-2802]

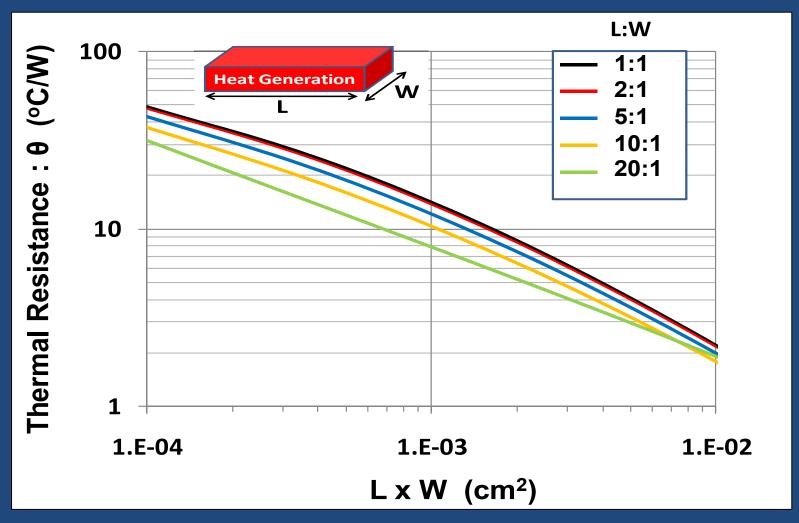

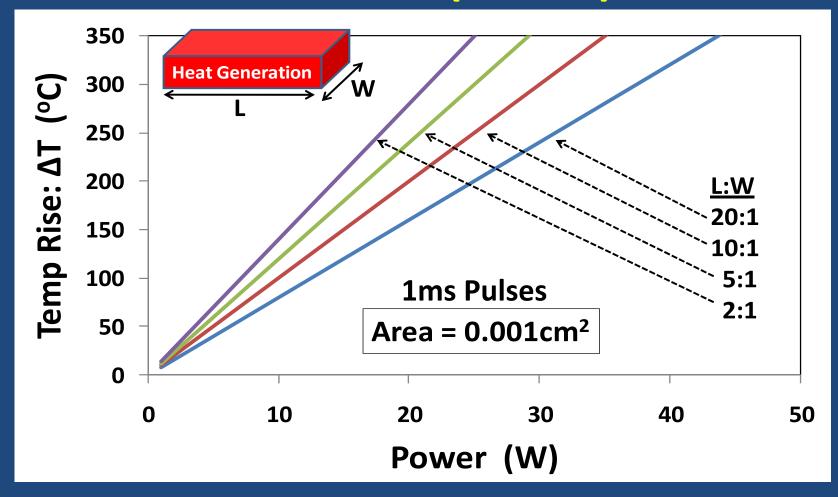

# T-SOA Modeled Thermal Resistance With 1ms Power Pulse

- ☐ Modeling of thermal resistance in agreement with experiment

- ☐ Modeling is slightly conservative, which is good!

- $\Box$  Thermal resistance  $\theta$  defines allowed power density (T-SOA)19

# **Thermal SOA (T-SOA)**

Notes:  $(1) 40W/0.001cm^2 = 40kW/cm^2$

(2) LDMOS devices can have ~ MW/cm² capability !!

(3)  $T_{\text{metal}} = T_J + \Delta T = 100^{\circ}\text{C} + 350^{\circ}\text{C} = 450^{\circ}\text{C}$

(4) Metal lifetime at 450°C is only ~100sec!

# What About Long-Term Reliability?

- Thus far ----

- ☐ We have learned how to generate: electrical safe operating areas (e-SOAs)

- ☐ We have learned how to generate:

Thermal safe operating areas: T-SOAs

- Remaining --- Long Term (10yr/105°C)

Reliability Safe Operating Areas: R-SOAs

- **Examples:**

- ☐ Hot Carrier Injection (HCI)

- Biased Temperature Instability (BTI)

- ☐ Time-Dependent Dielectric Breakdown (TDDB) <sup>21</sup>

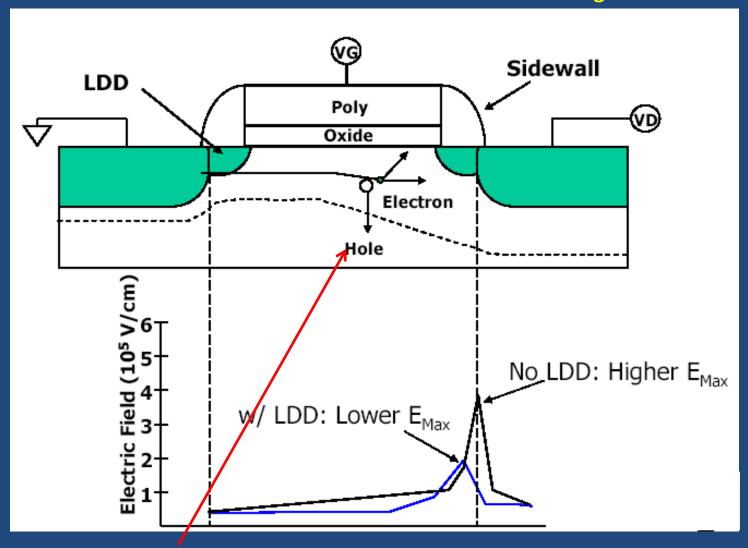

# Standard CMOS Hot Carrier Injection (HCI)

Note: Substrate current is a good proxy for HCI stress

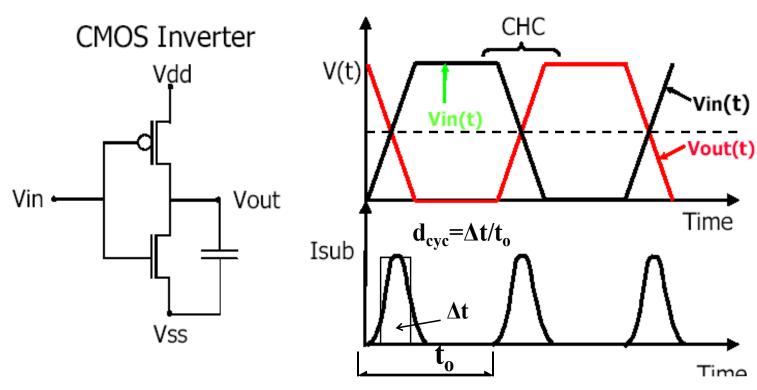

# R-SOA HCI During Digital Circuit Operation

Isub current is generated primarily during device switching

To minimize CHC:

- (1) Reduce slew rate of waveform

- (2) Reduce load capacitance

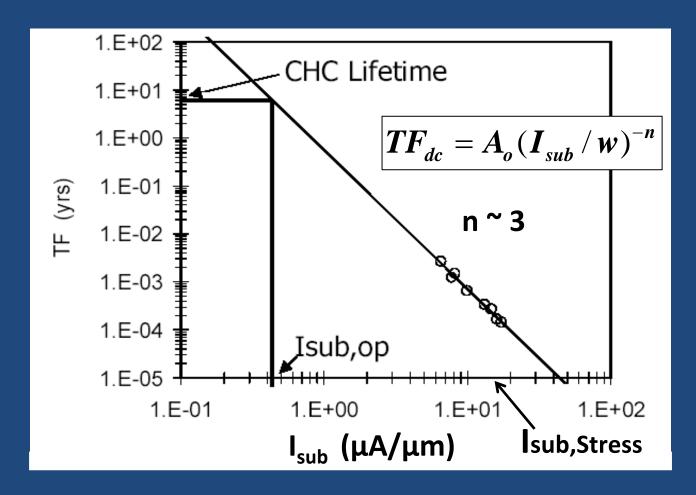

### **CHC Lifetime Versus Substrate Current**

Problem: DEMOS/LDMOS --- difficult/impossible to measure substrate current. Must take empirical stress data.

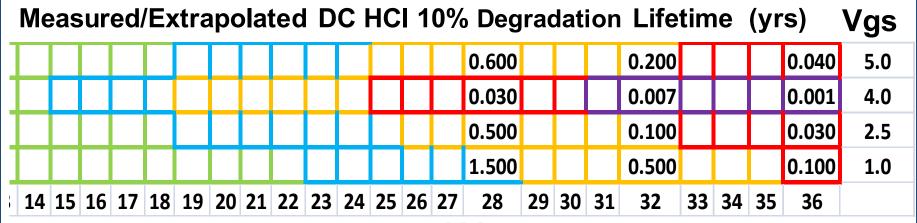

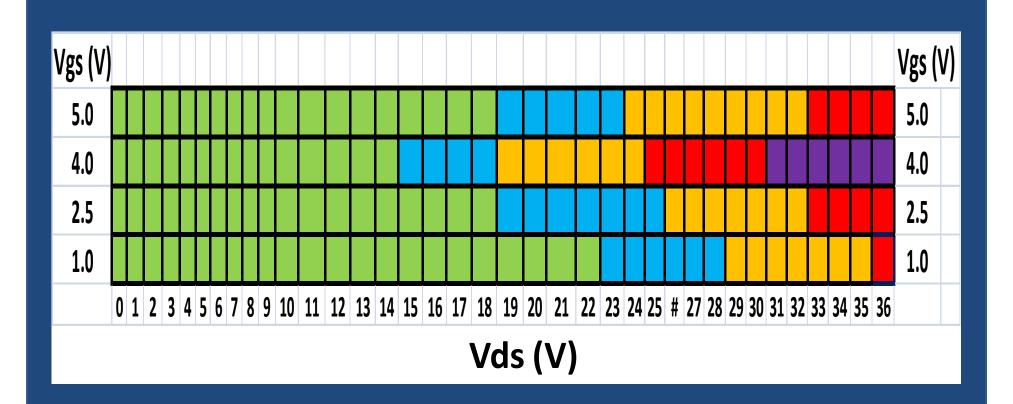

## **Example: Generation of HCI-SOA for 30V LDMOS**

### Vds

### Other Voltage Conditions can be Modeled:

$$AF_{Vds} = \exp[\beta(36V - V_{ds})]$$

where:  $\beta = 0.43/V$

$$AF_{Vgs} = \exp[-\alpha (4V - V_{gs})^{2}]$$

where :  $\alpha = \begin{cases} 1.5/V^{2} & \text{for } V_{gs} \leq 4 \\ 3.4/V^{2} & \text{for } V_{gs} \geq 4 \end{cases}$

> 10 yrs

| 1 yr |  | 0.1 yr |

|------|--|--------|

| 10yr |  | 1 yr   |

| 0.1 yr  |  | 0.01 yr  |  |  |

|---------|--|----------|--|--|

| 0.01 yr |  | 0.001 yr |  |  |

# **Example: Generation of HCI-SOA for 30V LDMOS**

Note: Keep-out regions (or very low-duty cycle regions) are clearly highlighted in the HCI-SOA

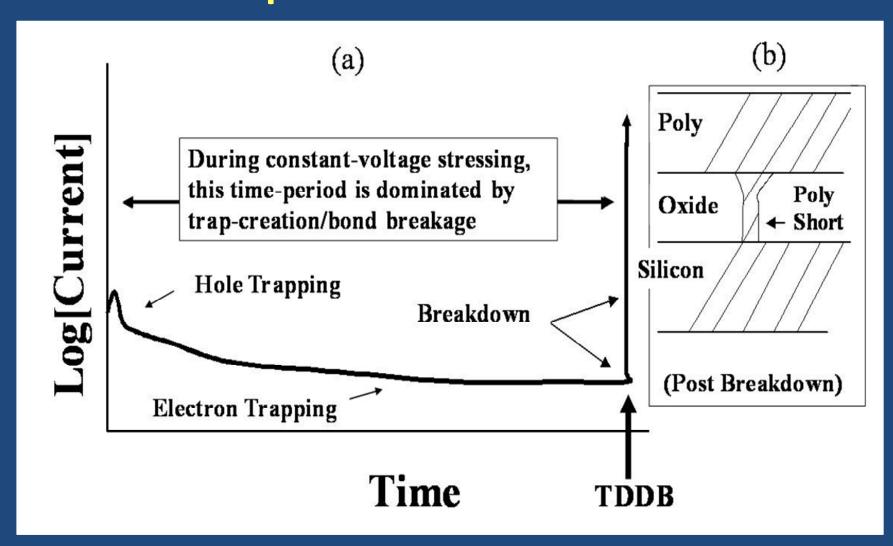

# R-SOA Time-Dependent Dielectric Breakdown

Note: All dielectrics will eventually breakdown

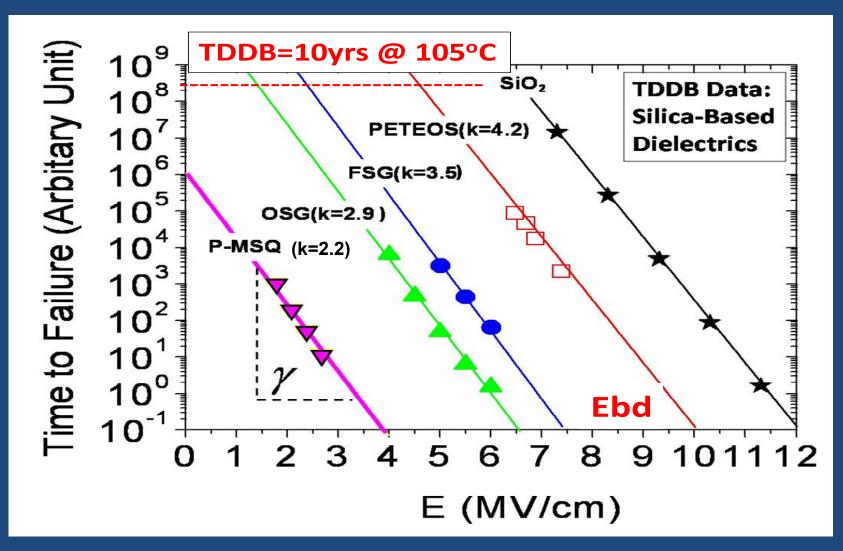

# R-SOA Time-Dependent Dielectric Breakdown Models

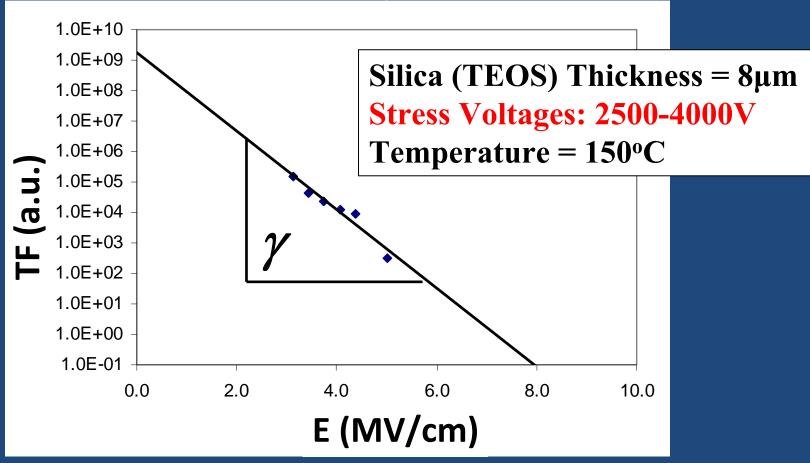

# R-SOA TDDB Data for Silica-Based Dielectrics

Breakdown Strength E<sub>bd</sub> changes but not slope γ

### **HV TDDB Data for Silica-Based Dielectrics**

### **HV** Isolation Capacitors

Observed:  $\gamma(150^{\circ}C) = 3.22cm / MV (for 8um - Stack)$

- HV TDDB Data (γ) Consistent with LV TDDB.

- No change in TDDB physics at high voltage.

# R-SOA TDDB-SOA for Gate Oxides

|            |                    |           |           |              |           |           | Reference    |

|------------|--------------------|-----------|-----------|--------------|-----------|-----------|--------------|

|            |                    |           |           | Reference    |           |           | Field        |

| Gate Oxide | Reference          | Reference | Reference | Average      | Reference | Reference | Acceleration |

| Thickness  | Area               | Temp      | Lifetime  | Failure Rate | Field     | Weibull   | Parameter: γ |

| (Angstrom) | (cm <sup>2</sup> ) | (°C)      | (Hr)      | (Fit)        | (MV/cm)   | Slope: β  | (cm/MV)      |

| 130 - 200  | 0.1                | 105       | 1.0E+05   | 10           | 4         | 3.0       | 4.0          |

| 50 - 129   | 0.1                | 105       | 1.0E+05   | 10           | 5         | 2.2       | 4.0          |

| 30 - 49    | 0.1                | 105       | 1.0E+05   | 10           | 6         | 2.0       | 3.6          |

| 20 - 29    | 0.1                | 105       | 1.0E+05   | 10           | 7         | 1.5       | 3.6          |

| 12 - 19    | 0.1                | 105       | 1.0E+05   | 10           | 7         | 1.2       | 3.3          |

$$AF = \left[\frac{dcyc}{(dcyc)_{ref}}\right] \bullet \left[\frac{Area}{(Area)_{ref}}\right]^{1/\beta} \bullet \exp[\gamma(E_{ox} - (E_{ox})_{ref})]$$

**Note: Assumes Good Quality Gate Oxide**

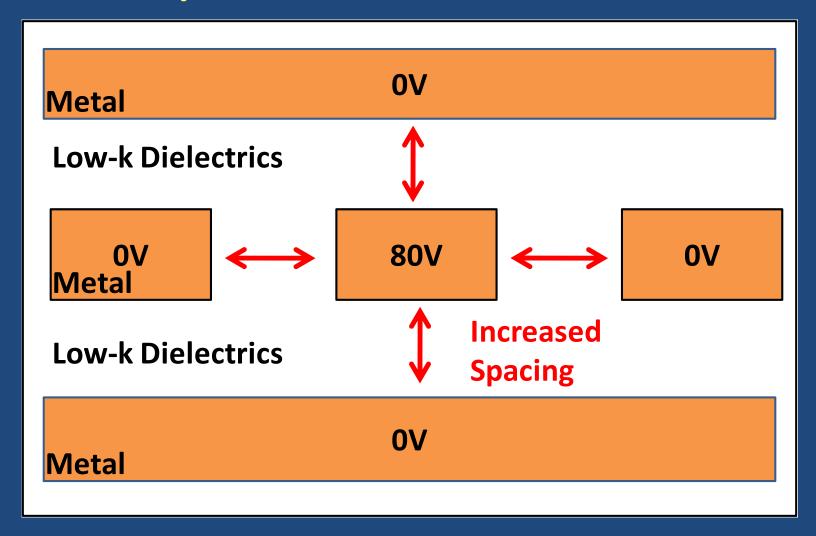

# R-SOA DEMOS/LDMOS Interconnect TDDB-SOA

TDDB-SOA (Interconnect Spacing):

(Space)<sub>min</sub> = 80V/(Ebd - 5MV/cm)

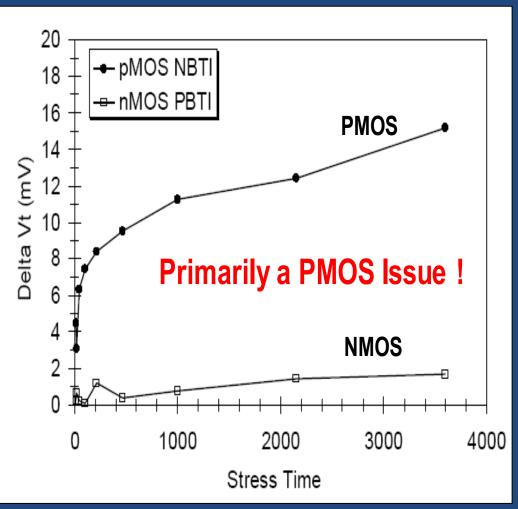

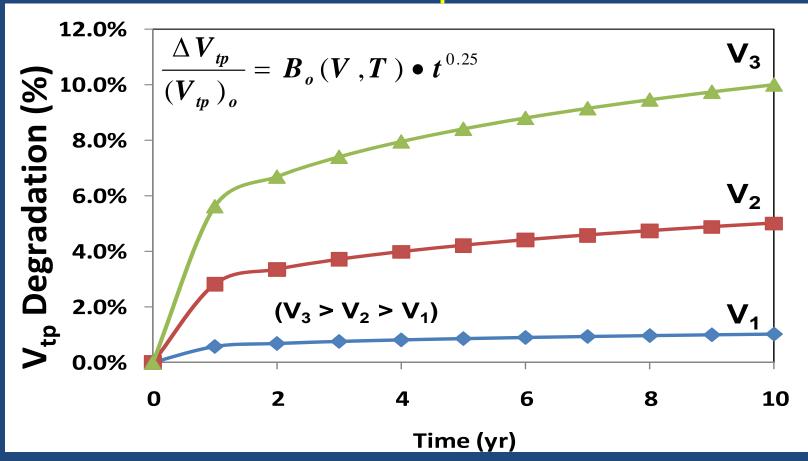

#### **NBTI-SOA**

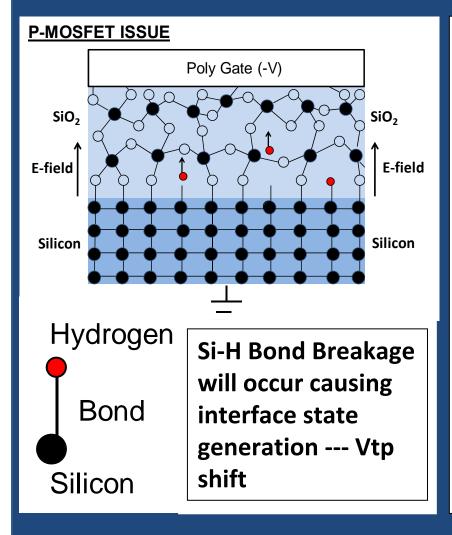

# **Negative Bias Temperature Instability**

#### **NBTI-SOA**

# **NBTI-Induced V<sub>tp</sub> Degradation**

- ☐ Most of shift occurs within 1<sup>st</sup> year of normal product use

- ☐ Can be accelerated to a few hours during HTOL for quick evaluation

- □ NBTI-SOA is presently handled by guard-banding at product level

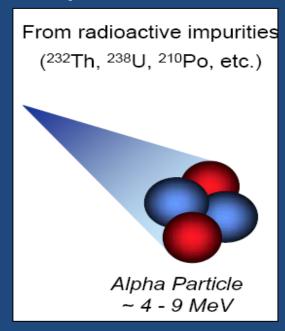

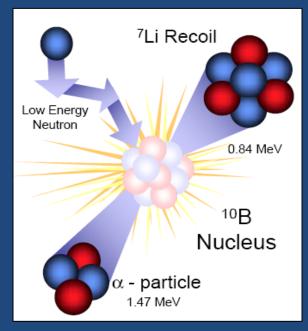

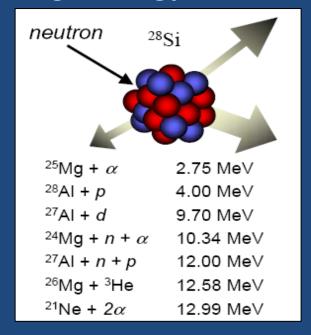

# **Single Event Upset (SEU)**

### **Alpha-Particles**

### **Thermal Neutrons**

### **High-Energy Neutrons**

#### **Important Reliability Considerations for SEU:**

- ☐ Materials selection which are low in radioactive impurities

- ☐ Removal of <sup>10</sup>B from BPSG process

- ☐ SER calculator/simulator

- ☐ Error correction

- ☐ Layouts to reduce multiple-bit errors

- ☐ SEU Induced Latch-up

# SEU Impact on HV

### **Devices:**

- ---Hard failures due to SEU induced latch-up

- --- Hard Failures due to TDDB in High-Voltage

**Capacitors**

### Conclusions

- ☐ The business demand for HV components is great

- ☐ HV components, such as DEMOS and LDMOS devices, can be safely integrated with LV CMOS when careful attention is given to Safe Operating Areas:

- --- e-SOA

- --- T-SOA

- --- R-SOA

- ☐ SEU-induced hard failures will need to be investigated more closely for HV devices